# **ESE 570 Design for Manufacture**

### **OVERVIEW**

Design Quality (Reminder) What is Design for Manufacturability? Modeling Process Variations Impact of Process Variations on Circuit Performance Parametric Yield Estimation Parametric Yield Optimization

## **DESIGN QUALITY**

-> ACHIEVE SPECIFICATIONS (Static & Dynamic) ->DIE SIZE ->POWER DISSIPATION

-> TESTABLE -> MANUFACTURABLE -> RELIABLE

## **DESIGN QUALITY cont.**

#### -> TESTABLE

+ generation of good test vectors

+ availablity of reliable test fixture at speed

+ design of testable chip

-> MANUFACTURABLE

+ functional yield

+ parametric yield

->RELIABLE

- + premature aging (Infant mortality)

- + ESD/EOS

+ latchup

- + on-chip noise and crosstalk

- + power and ground bouncing

### WHAT IS DESIGN FOR MANUFACTURABILITY?

**Design goal:** All fabricated circuits meet all performance specs under all fab and operating conditions.

**Impediments:**

- **1. Random variations in fabrication process.**

- 2. Random variations in operating conditions, e.g. V<sub>DD</sub>, T<sub>ambient</sub>.

- 3. Less than full chip testability (controllability and observability).

### WHAT IS DESIGN FOR MANUFACTURABILITY?

**DFM Practice:**

**1. Consider effects of random fabrication parameters and operating conditions early in the design process.**

2. Design and layout done to reduce sensitivity to these variations.

a. Design to performance specs with sufficient margins.b. Satisfy Design Rules with some margin.

**3. Design for Testability.**

**DFM Metrics:**

- **1. Functional yield.**

- 2. Parametric yield.

- 3. Worst-case performance.

- 4. Test fault coverage.

## **VLSI CAD Supports Design for Manufacturability**

### CATAGORIES OF CAD TOOLS

- 1. High Level Synthesis (HDLs)

- 2. Logic Synthesis

- 3. Circuit Optimization

- a. transistor sizing for min delays

- b. process variations

- c. statistical design

- 4. Layout

- a. floorplanning

- b. place & route

- c. module generation

- d. automatic cell placement and routing

- 5. Layout Extraction

- 6. Simulation (SPICE for circuit-level simulation)

- 7. Layout Schematic Verification

- 8. Design Rule Check

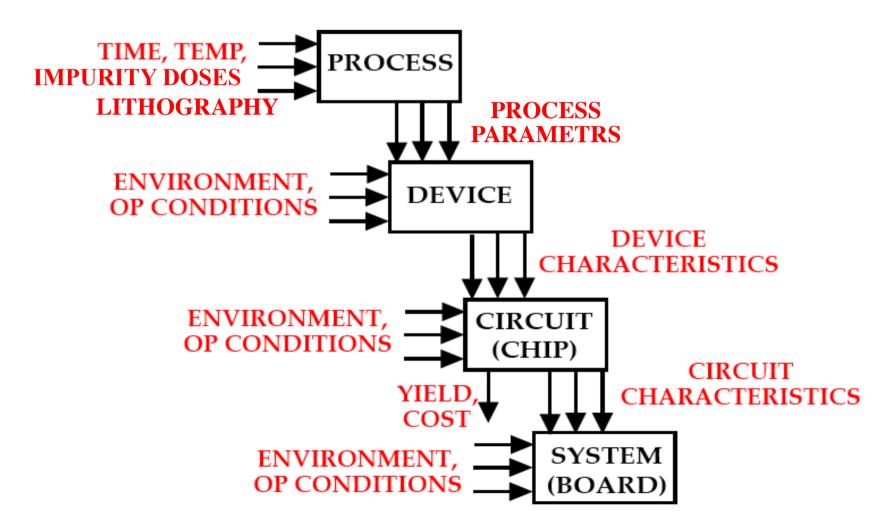

### RELATIONSHIP BETWEEN PROCESS/DEVICE PARAMETERS AND CIRCUIT/SYSTEM PERFORMANCE

## **MODELING PROCESS VARIATIONS**

$$I_d = \mu C_{ox} \left(\frac{W}{L}\right) f(V_{DS}, V_{GS}, V_T)$$

$I_{d-actual} \neq I_{d-design}$  due to variations in  $\mu$ ,  $t_{ox'}$  W/L and  $V_{T}$

$I_{d-actual} \neq I_{d-design} =>$  variations in logic levels, delay times, power dissipation.

# TO MAKE CIRCUIT LESS SENSITIVE TO CIRCUIT/PROCESS PARAMETERS

1. Make critical devices larger, i.e. increase L and W, keeping W/L constant.

2. Careful orientation of key transistors in layout, e.g. to take advantage of oxide gradients to keep  $t_{ox}$  constant.

$$\begin{bmatrix} x_1 \\ x_2 \\ \cdot \\ \cdot \\ x_n \end{bmatrix} = \begin{bmatrix} d_1 \\ d_2 \\ \cdot \\ \cdot \\ d_n \end{bmatrix} + \begin{bmatrix} s_1 \\ s_2 \\ \cdot \\ \cdot \\ s_n \end{bmatrix} d_i = designable or controllable parameter set set s_i = random variation or noise parameter set s_i = random variation or noise parameter set actual = design + random \Delta$$

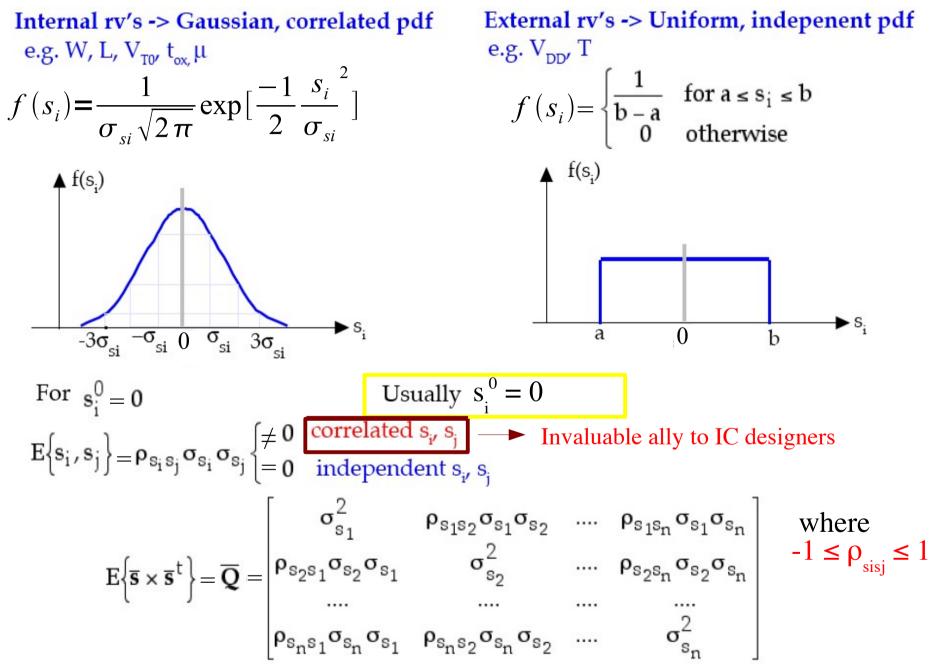

## **MODELING PROCESS VARIATIONS cont.**

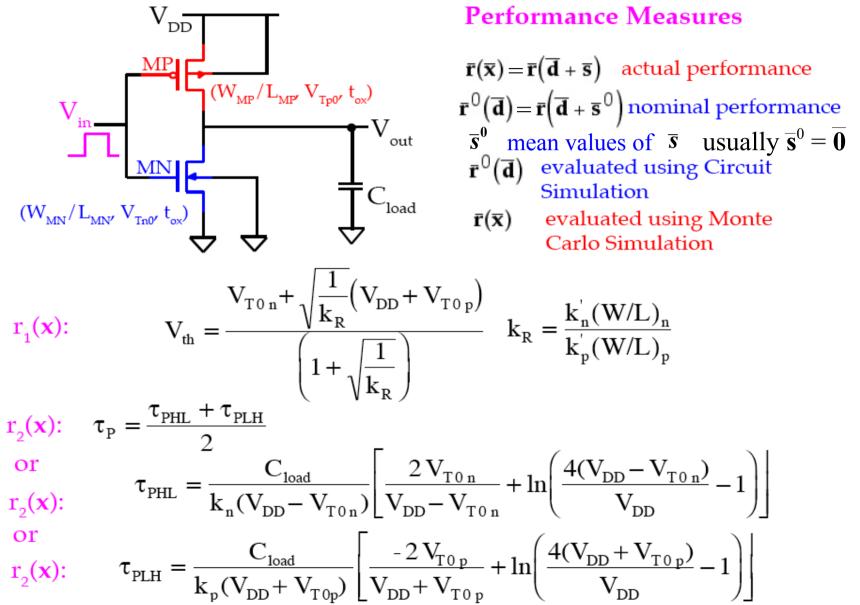

### **IMPACT OF PROCESS VARIATIONS ON CIRCUIT PERFORMANCE MEASURES**

### **IMPACT OF PROCESS VARIATIONS ON CIRCUIT PERFORMANCE MEASURES cont.**

$\begin{array}{l} r = r(\overline{x}) = r(\overline{d} + \overline{s}) & \text{actual performance - random variable} \\ r^{0}(\overline{d}) = r(\overline{d} + \overline{s}^{0}) & \text{nominal or designed performance - deterministic variable} \end{array}$

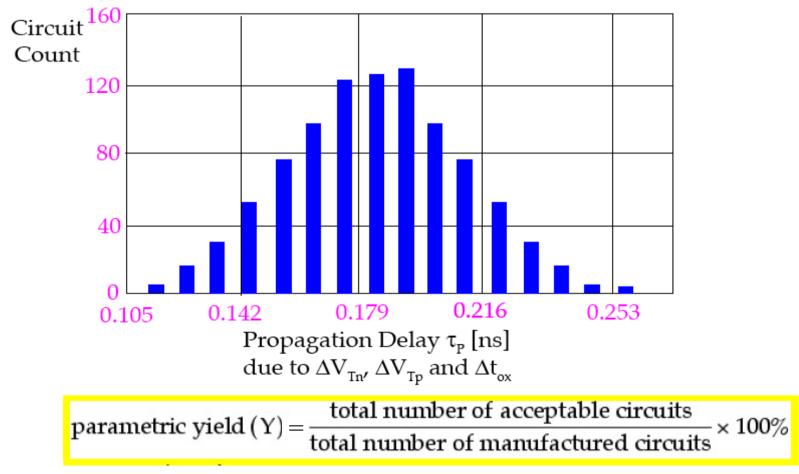

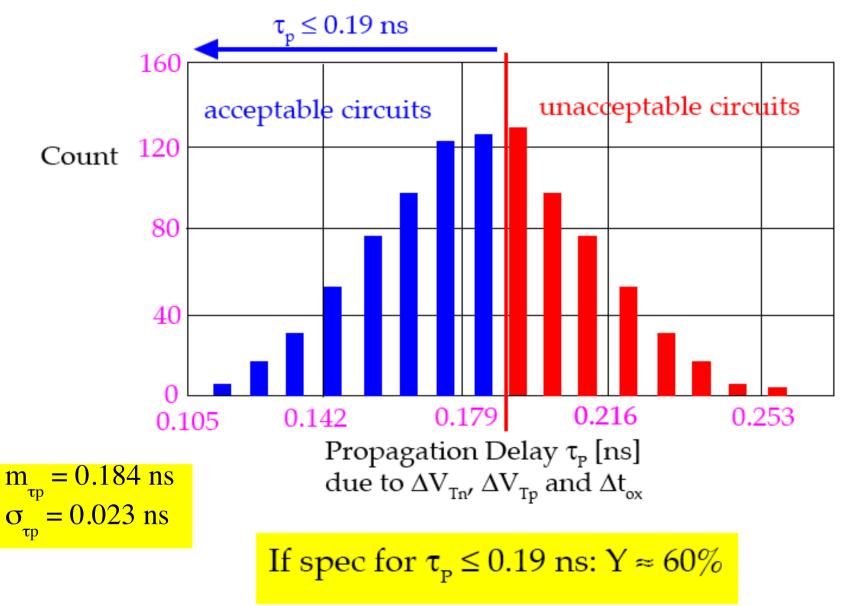

Each statistical circuit performance measure is illustrated using a histogram

### **IMPACT OF PROCESS VARIATIONS ON CIRCUIT PERFORMANCE MEASURES cont.**

# Some Real Defects in Chips

- Processing defects

- Missing contact windows

- Parasitic transistors

- Oxide breakdown

- Material defects

- Bulk defects (cracks, crystal imperfections)

- Surface impurities (ion migration)

- Time-dependent failures (Age defects)

- Dielectric breakdown

- Electromigration

- Packaging failures

- Contact degradation

- Seal leaks

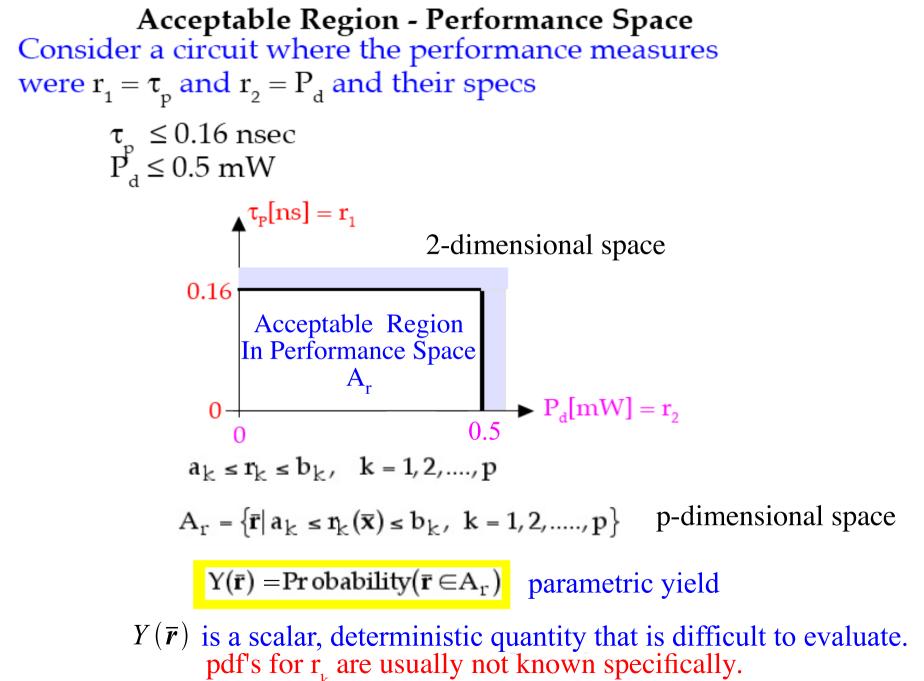

## **PARAMETRIC YIELD ESTIMATION**

### **PARAMETRIC YIELD ESTIMATION cont.**

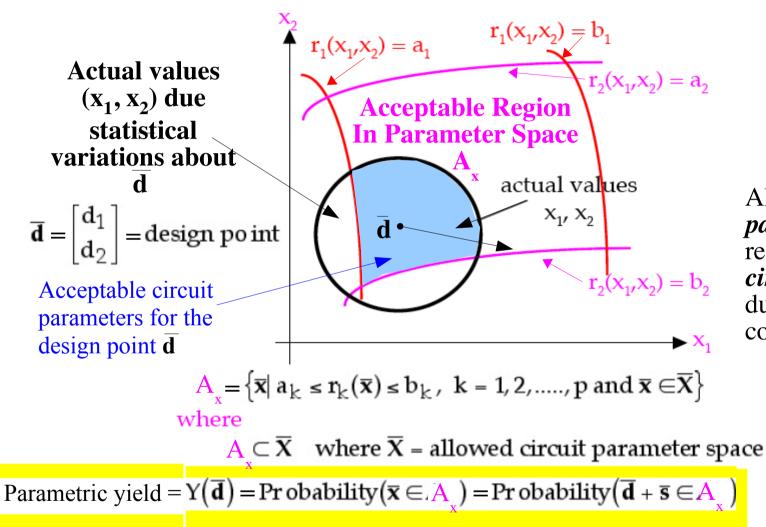

Acceptable Region - Parameter Space

Allowed *circuit parameter values* restricted to subset of *circuit parameter space* due to physical considerations.

Y is a scalar, deterministic quantity. Monte Carlo sampling is the most often used method to estimate Y.

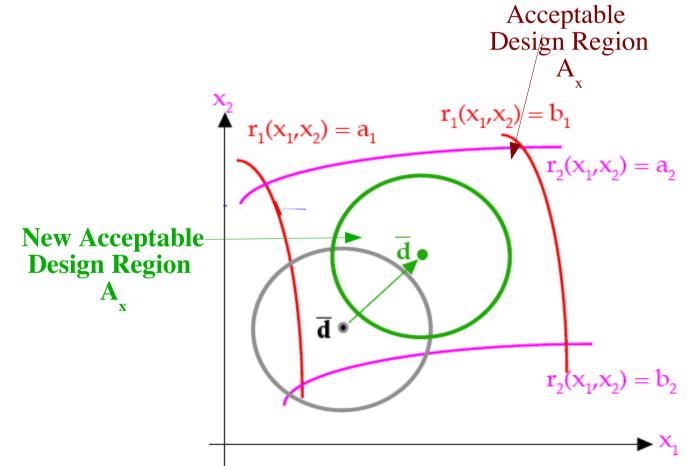

### PARAMETRIC YIELD MAXIMIZATION

#### 1. Monte Carlo Based Methods

$Y(\overline{\mathbf{d}}) = \Pr \text{ obability}(\overline{\mathbf{x}} \in A_{\times}) = \Pr \text{ obability}(\overline{\mathbf{d}} + \overline{\mathbf{s}} \in A_{\times})$

a. Compute  $Y(\bar{d})$  using Monte Carlo Simulation

b. Determine  $\overline{\mathbf{d}}$  to maximize  $Y(\overline{\mathbf{d}})$

2. Design Centering Method

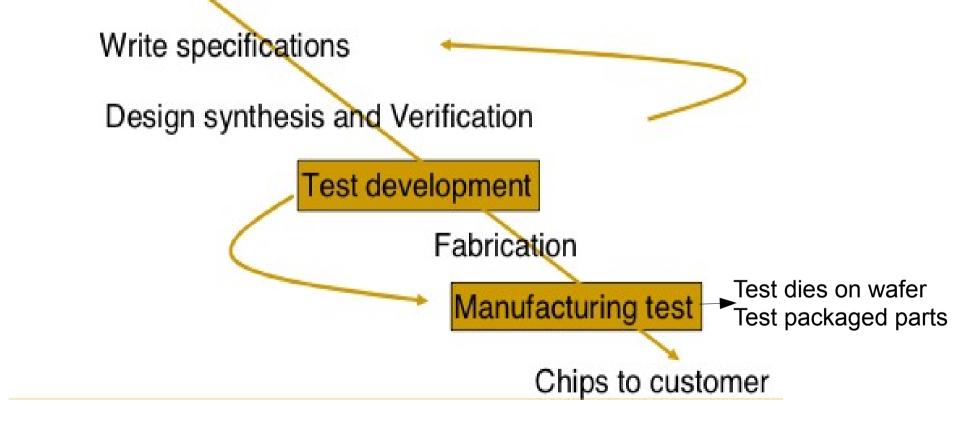

Customer's need

Determine requirements

# Types of Manufacturing Tests

- Characterization Testing

- Used to characterize devices and performed through production life to improve the process, hence yield

- Production testing

- Factory testing of all manufactured chips for parametric faults and for random defects.

- The test patterns may not cover all possible functions and data patterns but must have a high fault coverage of modeled faults.

- The main driver is cost, since every device must be tested. Test time must be absolutely minimized.

- Only a go/no-go decision is made.

- Burn-In testing

- Ensure reliability of tested devices by testing.

- Detect the devices with potential failures.

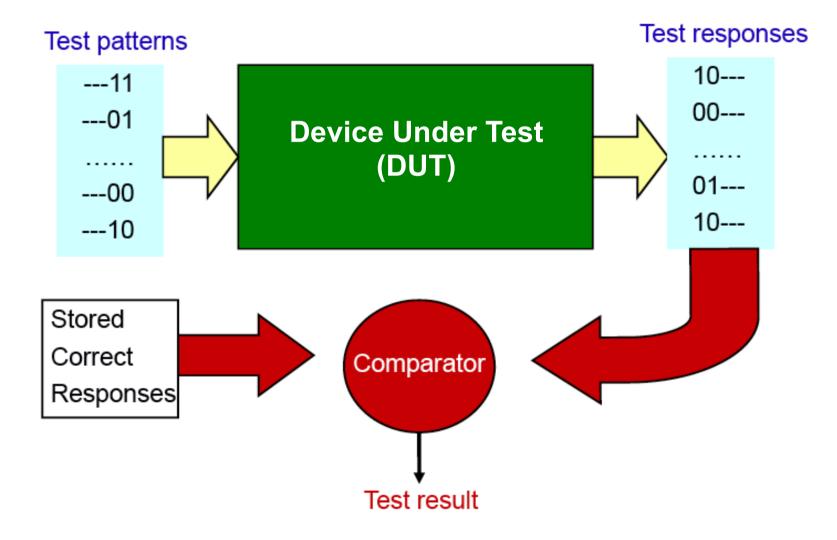

# **Testing Principle**

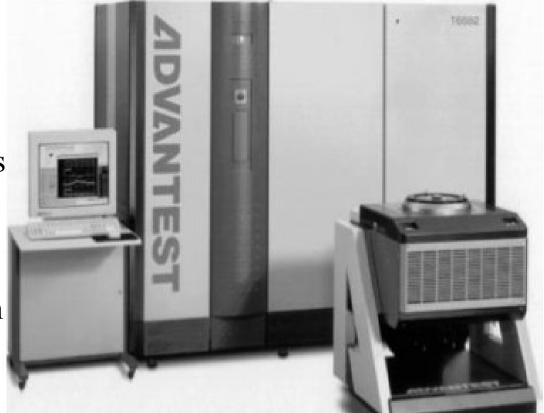

# EXAMPLE ADVANTEST Model T6682 ATE

#### Consists of

- Powerful computer

- Powerful DSP for analog testing

- Probe head: actually touches the bare dies or packaged chips to perform fault detection experiments

- Probe card: contains electronics to measure chip pin or pad

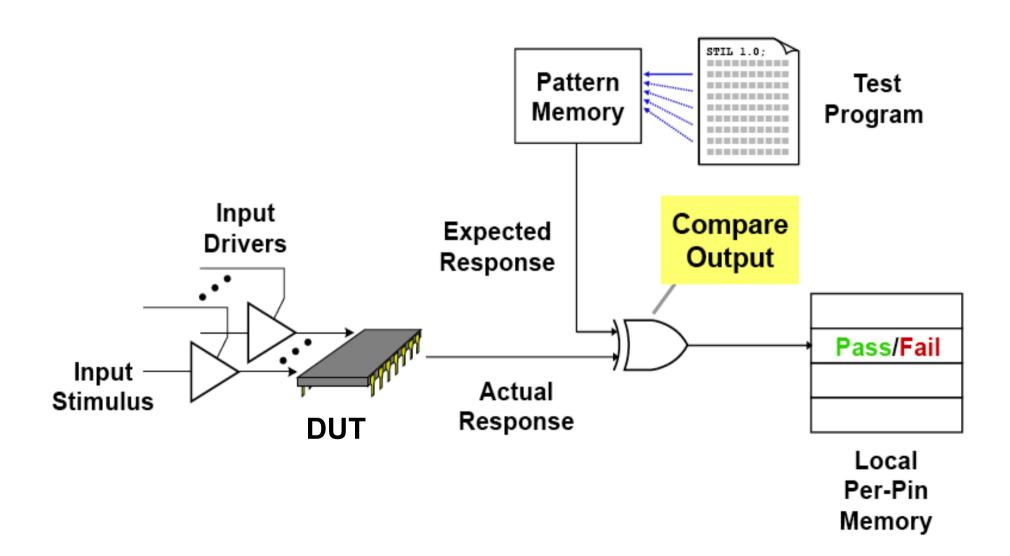

## **ATE Test Operation**

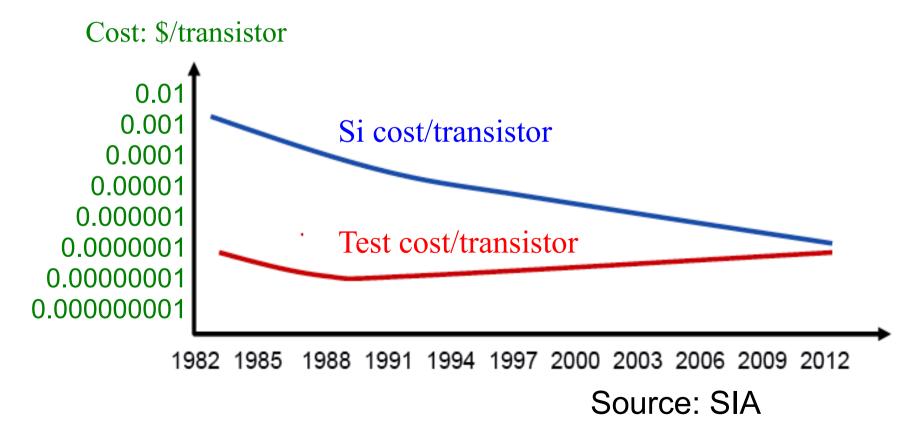

## Test Cost Trends

Two key factors are changing the way of VLSI ICs testing

- The manufacturing test cost has been not scaling

- The effort to generate tests has been growing geometrically along with product complexity

## Defect, Fault, and Error

#### **Defect (imperfection in hardware):**

A defect in an electronic system is the unintended difference between the implemented hardware and its intended design.

#### **Error:**

A wrong output signal produced by a defective system is called an error. An error is an "effect" whose cause is some "defect".

#### Fault (imperfection in function):

A representation of a "defect" at the abstracted function level is called a fault.

# **Observability & Controllability**

- Observability: ease of observing a node by watching external output pins of the chip

- Controllability: ease of forcing a node to 0 or 1 by driving input pins of the chip

- Combinational logic is usually easy to observe and control

- Sequential logic or finite state machines can be very difficult, requiring many cycles to enter desired state

- Good observability and controllability reduces number of test vectors required for manufacturing test.

- Reduces the cost of testing

- Motivates design-for-test

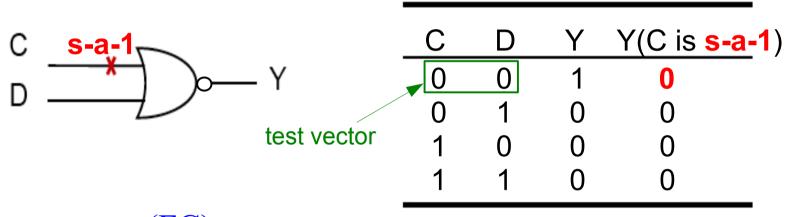

## **Common Fault Models**

**Single stuck-at faults**

Transistor open and short faults

Memory faults

PLA faults (stuck-at, cross-point, bridging)

Functional faults (processors)

Delay faults (transition, path)

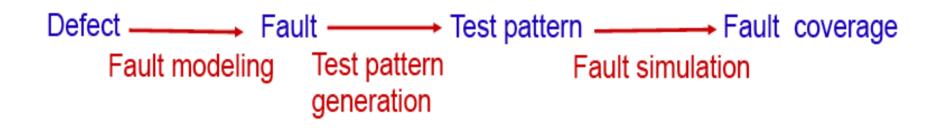

## **Test Process**

What faults to test (*fault modeling*)?

How are test patterns obtained (*test pattern generation*)?

How is test quality (fault coverage) measured (*fault simulation*)?

How are test vectors applied and results evaluated (ATE/BIST)?

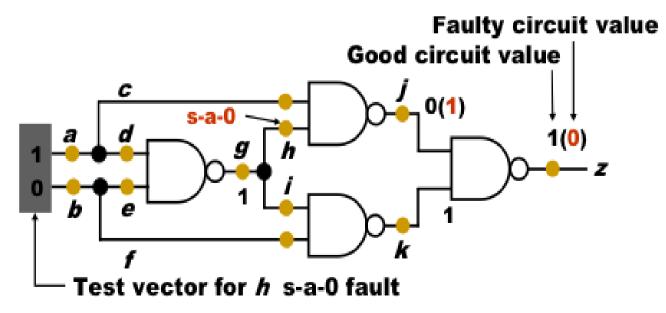

## Single Stuck-at Fault

Three properties define a single stuck-at fault

Only one line is faulty

The faulty line is permanently set to 0 or 1

The fault can be at an input or output of a gate

Example: XOR circuit has 12 fault sites (•) and 24 single stuck-at faults

Kenneth R. Laker, University of Pennsylvania, updated 27Apr15

## **The Test Problem**

Given a set of faults in the DUT, how do we obtain a certain (small) number of test patterns which guarantees a certain (high) fault coverage?

### Fault coverage (FC)

- The measure of the ability of a test (a collection of test patterns) to detect faults that may occur on the DUT

- $FC = \frac{Number of detected faults}{Number of possible faults}$

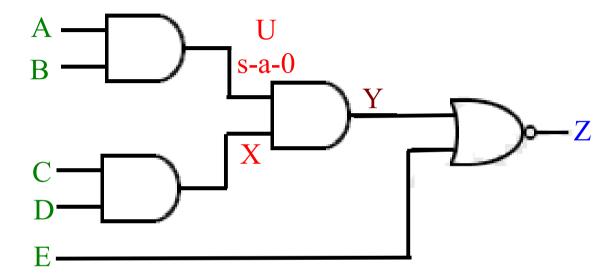

### **AUTOMATIC TEST-PATTERN GENERATION (ATPG)**

Determine the input pattern that exposes an s-a-0 fault occurring at node U at the output Z.

- a. Choose an input pattern that sets U = 1, i.e. A = B = 1 controllability.

- b. The fault at U needs to propagate to Z to be observed, i.e. Y = U iff X = 1 and Z = U if E = 0.

- c. **X** = **1** => C = D = 1.

- d. The (unique) test vector can now be assembled: A = B = C = D = 1, E = 0.

# **Design for Test**

\* Design the chip to increase observability and controllability.

- ★ If each register could be observed and controlled, test problem reduces to testing combinational logic between registers.

- \* Better yet, logic blocks could enter test mode where they generate test patterns and report the results automatically.

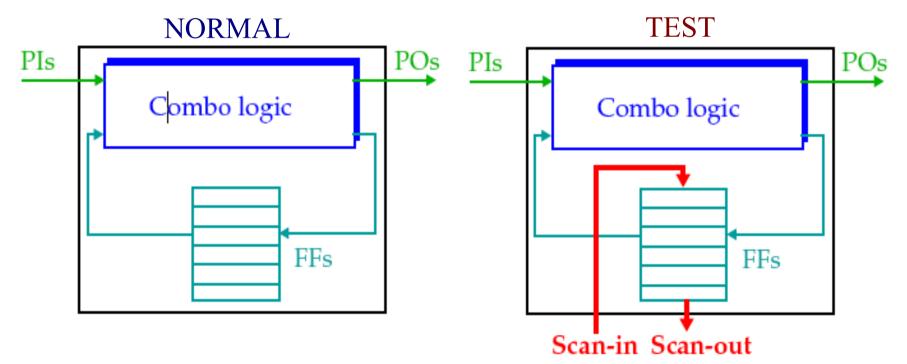

## **Scan Based Testing**

#### Scan test is to obtain control and observability for FFs.

- It reduces sequential Test Pattern Generation circuits (TPG) to combinational TPG circuits.

- With Scan, a synchronous sequential circuit works in two modes.

Normal mode and Test mode:

In **test mode**, all **FFs** are configured as a shift register, with Scan-in and Scan-out routed to a (possibly dedicated) Pin-IN (PI) and Pin-OUT (PO).

## **Scan Based Testing**

Convert each flip-flop to a scan register SCAL Flop SI D Costs one extra multiplexer Q **SCAN** SI Normal mode: flip-flops behave as usual **SCAN** OUT Scan mode: flip-flops behave as shift register **SCAN** scan-in Contents of flops can be scanned out and new D- inputs Q- outputs values scanned in Logic Cloud Logic Cloud

scan-out

CLK

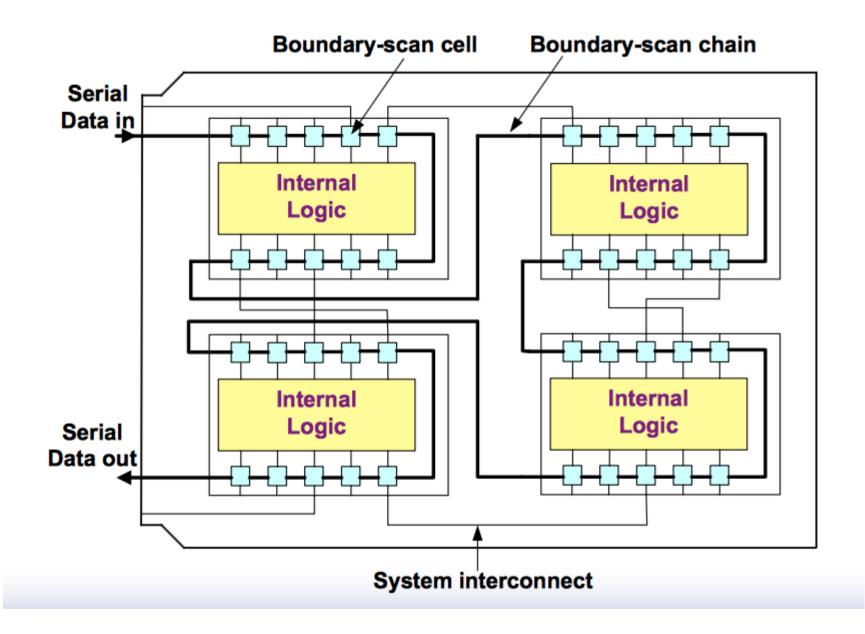

### **Boundary Scan for Board Test**

## **Some Important Boundary Standards**

- Digital Boundary Scan (IEEE 1149.1)

- Analog Boundary Scan (IEEE 1149.4)

- Boundary Scan for Advanced Networks (IEEE 1149.6)

- Embedded Core Test Standard (IEEE 1500)